隔月でお送りしているRISC-V WG主催Webセミナーも、本年度締めの回となる第11回を迎えました。

今回は一般社団法人RISC-V協会 代表理事 河崎 俊平様に「RISC-VやDARPA Googleのオープンロードは、FPGA開発に何をもたらしたのか?」と題し、ご講演いただきます。皆さま奮ってご参加ください。

RISC-V WG主査 小檜山智久

一般社団法人RISC-V協会 代表理事 河崎 俊平氏

2013年以降、アーキテクチャ、IP、ボード、FPGAをオープンソースEDAツールで設計するトレンドが存在しています。 こうした取り組みの多くは米国国防省DARPAの働きによるものです。 2010年ごろに、ムーア法則が終焉を迎えたという話がありました。これにより半導体の指数関数的成長(性能、コスト、電力)のトレンドが終わったとされる中、米国の半導体業界のベテランがDARPAに招聘され、どのように電子産業の指数関数的成長率を継続するかを議論したのです。彼らが着目したのは、ムーア法則と同じ指数関数的成長率を持つのは「オープンソースのネットワーク効果」というもので、ネットワーク、ブラウザ、などの開発において類似の指数関数的な成長が見られるため、これを半導体の設計開発にも適用したらいいというある意味、専門家が考える発想でなく、初心者が考える発想でした。

FPGA開発、ボード開発、チップ設計などもオープンソースEDAツールで実施できるようになっていて、これらの動きについてもお話しします。

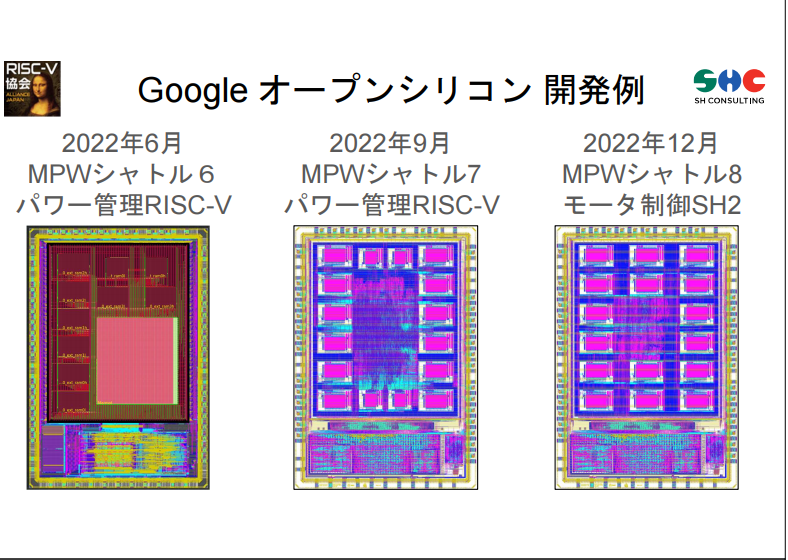

2022年2月にGoogle社よりお誘いを受け、上記スライドに示すチップをオープンソース技術を活用して、あるいはクローズソース技術をオープンにすることで、マルチプロジェクトウエハ(MPW)で3回テープアウトさせていただきました。うち1つはGoogle社の費用でチップ試作をさせていただくことになっています。3世代テープアウトをするうちに、試作ごとに論理部分の面積比率が減り、RAMが18KB → 28KB → 32KBと増加していることに気付きました。チップ設計ノウハウが貯まり同じ論理を少ない面積で設計できるようになったこともありますが、専用回路で実装していた機能をソフトで定義できるので、論理回路→メモリに置き換わる潮流を暗示しているのではないかと思いました。3つのチップの顔を見ていて、機能を論理回路で実現するとともに、機能をソフトで実現する時代のトレンドに設計者が合わせ、これがRAM容量増加に現れているかと思いました。

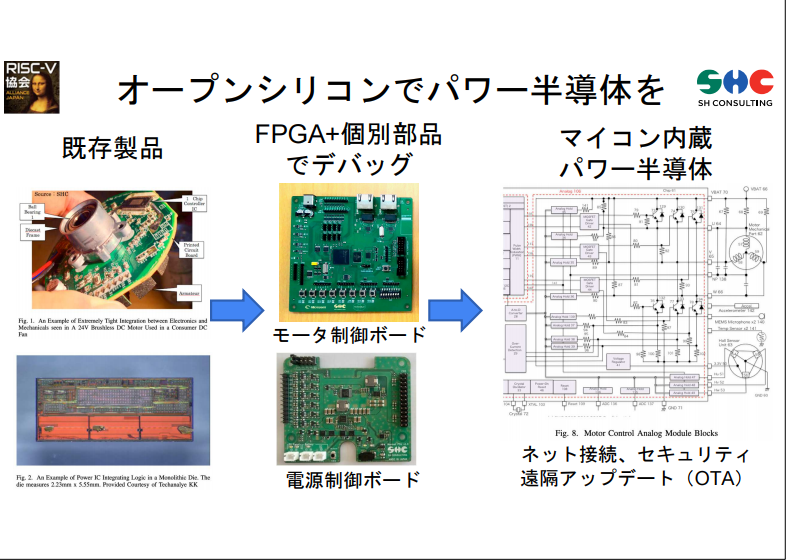

オープンソースEDAツールとオープンアーキテクチャ、オープンIP、オープンボードIP、オープンFPGA設計ツールによって、昔はお金がかかった設計作業が安価にできるようになっています。 現在は、多大な資本を集約したグローバルIT企業による寡占化で、日本企業が活躍できる場がなくなったと思われています。SHコンサルティング株式会社では、2017年に、ある新進企業に資金提供いただき、モーター制御用FPGAボードを試作しました。KIKADというオープンソースのボード設計ツールに習熟するのに時間がかかり、予定納期より1年近くもボード入荷が遅れ大変叱られました。 2018年に、ボード設計できればチップ設計もできるはずだと、台湾のファンドリと議論して、40ナノメータなどのプロセスで半導体を試作製造しようとすると、高額の資金が必要だと知りました。

ソフトウエア技術やアナログ、RF、パワーなどの技術を、半導体技術と複合することで試作費用が安い太線プロセスでも半導体製品を事業化をできます。 ESP32を作っている中国のEspressif社は40ナノメータプロセスを使っているとされています。WiFiソフトウエアなどの技術を集積しています。英国のFTDI社 Future Technology Devices International Ltdではインタフェースチップを事業化していますが、同社は90ナノメータのプロセスを使い、ソフトウエア技術と抱き合わせて事業展開をしています。

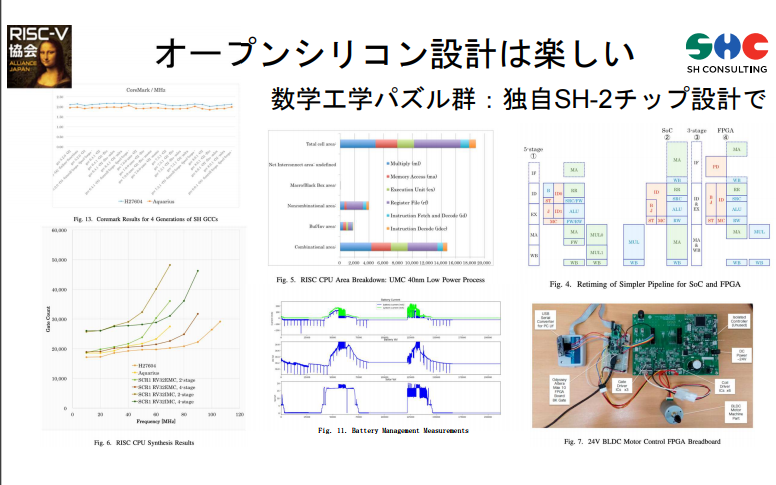

結論として、従来アナログ回路と有限状態機械(FSM)で実現されていたモータ制御や電源制御チップにマイコンを内蔵させソフトウエアで機能を定義するチップを開発することにしました。 2013年ごろに独自SHチップを製品化するSHコンサルティング(株)を結成しました。2014年にSH特許が満了することを見越して、独自のSHを設計し始めました。だが、本当の理由は、シリコン設計は楽しいからそうしたのです。 このようなお話を具体例を挙げてプレゼンする予定です。

Copyright © Japan Embedded Systems Technology Association All Rights Reserved.